1. 프로세스(Process)의 개념

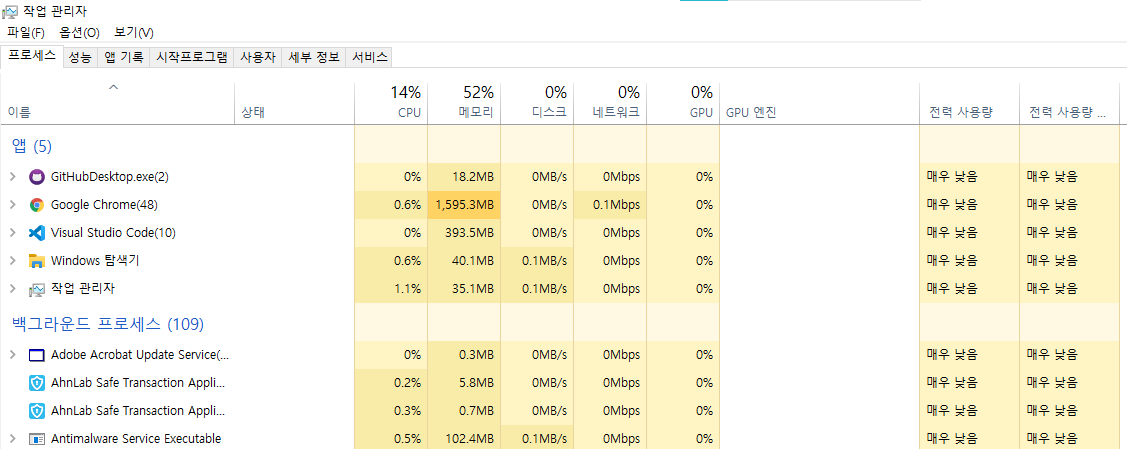

Windows 에서의 작업 관리자에서 확인 가능한 프로세스

Windows 에서의 작업 관리자에서 확인 가능한 프로세스

프로세스(process)는 컴퓨터에서 실행되고 있는 컴퓨터 프로그램을 말합니다. OS는 프로그램이 실행되면 디스크에 있는 데이터를 메모리에 적재합니다.

2. 프로세스의 구조 및 특징

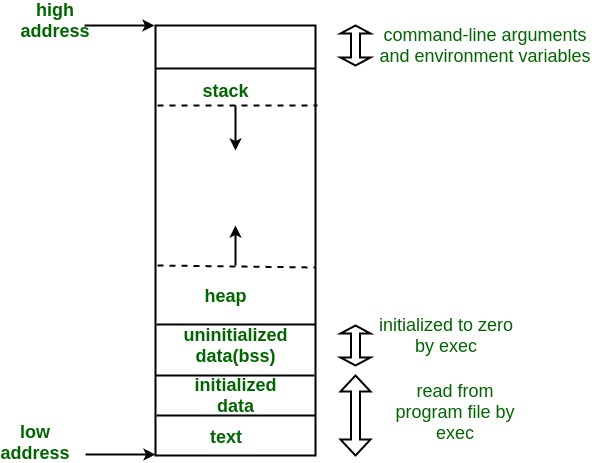

프로세스 구조

프로세스 구조

- 프로세스는 위와 같이 생겼으며, 해당 요소들을 가장 낮은 주소에 위치한 것부터 설명하면 아래와 같습니다.

- 텍스트(text) : 수행하는 프로그램 코드가 들어가 있는 영역

- 데이터 섹션(data) : 전역 변수들을 수록. 초기화 된 전역 변수와 초기화 되지 않은 전역 변수 영역이 나눠져 있으며, 초기화 되지 않은 값이 있는 영역을 bss 라고 함

- 힙(heap) : 동적할당에 사용

- 스택(stack) : 함수의 매개변수, 복귀 주소와 로컬 변수와 같은 임시 자료를 가지는 영역

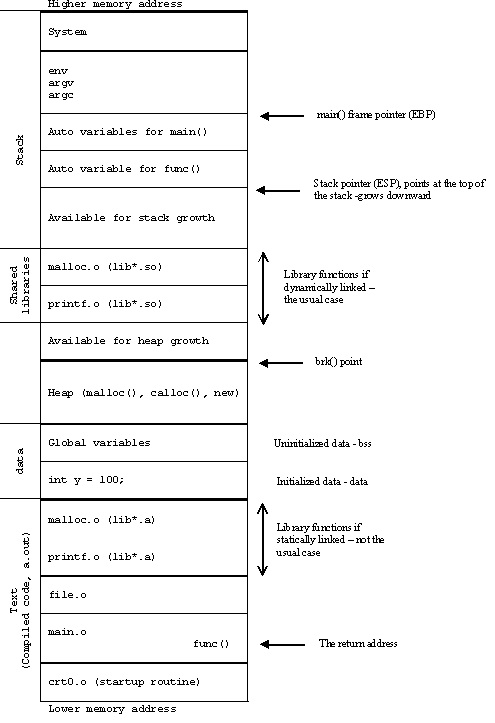

프로세스 구조 2

프로세스 구조 2

3. 프로세스 제어 블록(Process Control Block, PCB)

프로세스 제어 블록(Process Control Block, 줄여서 PCB)은 프로세스를 관리하기 위한 정보를 포함하는 OS 커널의 자료 구조입니다.- OS는 프로세스의 생성과 동시에 고유한 PCB 를 생성합니다.

- PCB가 프로세스의 중요한 정보를 포함하고 있기 때문에, 일반 사용자가 접근하지 못하도록 보호된 메모리 영역 안에 위치합니다.

-

프로세스는 수행할 차례가 되면, CPU를 할당받아 작업을 처리합니다. 작업을 처리하던 도중 프로세스의 시간이 모두 경과되거나 인터럽트가 발생하는 등의 프로세스 전환이 발생하면, 진행하던 작업을 저장하고 CPU 를 반환합니다. 이 때, 수행하던 프로세스 관련 데이터들을 PCB 에 저장합니다. 그리고 다시 프로세스의 수행 차례가 와서 CPU 를 할당받게 되면, PCB 에 저장되어있던 내용을 불러와 이전에 종료됐던 시점부터 다시 작업을 수행합니다. 이렇게 사용하던 프로세스의 데이터를 PCB에 저장하고, 실행할 프로세스의 데이터를 PCB에서 불러오는 과정을

Context Switching이라고 합니다. - PCB 에 저장되는 정보는 아래와 같습니다.

- 프로세스 식별자(Process ID, PID) : 프로세스 식별번호

- 프로세스 상태 : new, ready, running, waiting, terminated 등의 상태를 저장

- 프로그램 카운터 : 프로세스가 다음에 실행할 명령어의 주소

- CPU 레지스터

- CPU 스케쥴링 정보 : 프로세스의 우선순위, 스케줄 큐에 대한 포인터 등

- 메모리 관리 정보 : 페이지 테이블 또는 세그먼트 테이블 등과 같은 정보를 포함

- 입출력 상태 정보 : 프로세스에 할당된 입출력 장치들과 열린 파일 목록

- 어카운팅 정보 : 사용된 CPU 시간, 시간제한, 계정번호 등

4. 물리 메모리와 가상 메모리

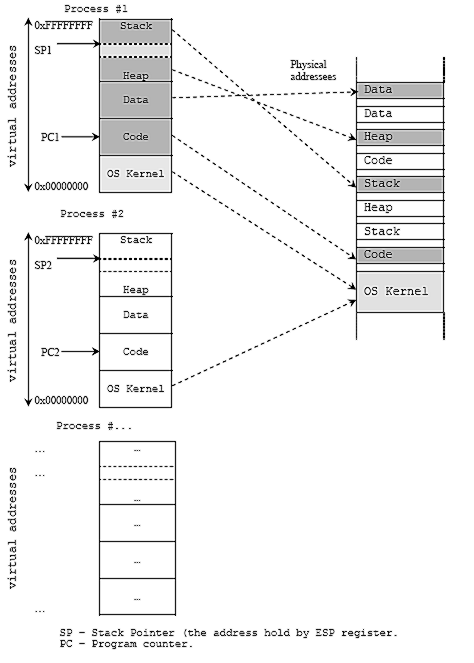

물리 메모리와 가상 메모리

물리 메모리와 가상 메모리

- 프로그램을 수행하는 입장에서 본 메모리는

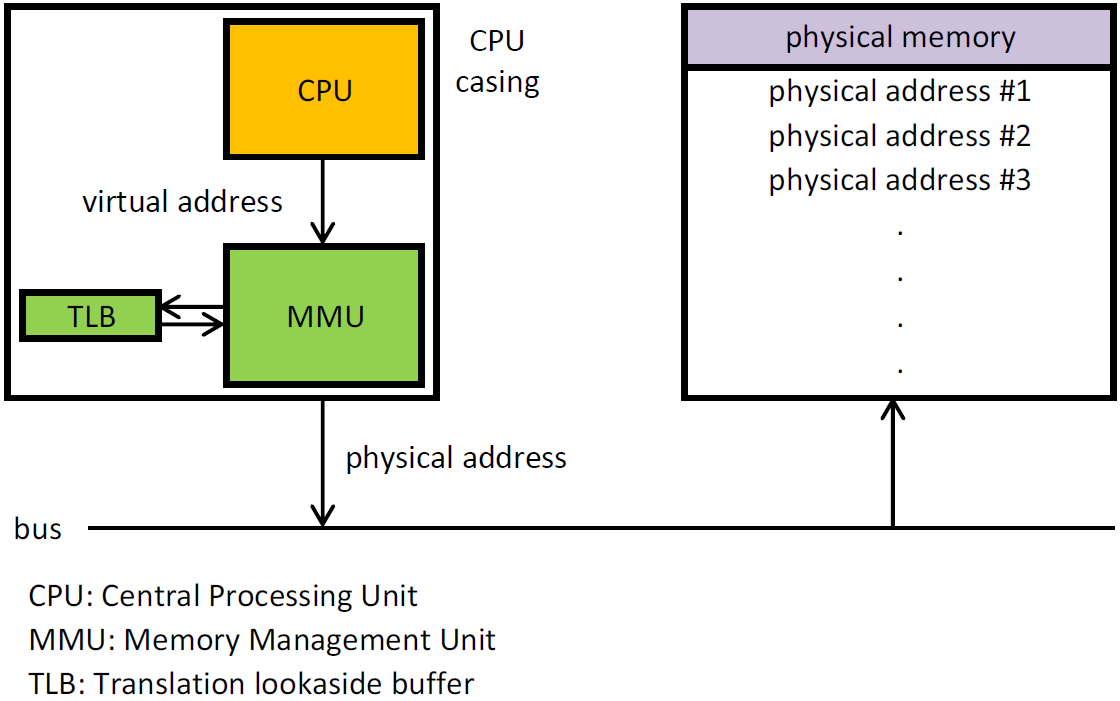

가상 메모리(Virtual Memory)로 실제 데이터가 위치하는 DRAM, 즉물리 메모리(Physical Memory)는 다릅니다. 가상 주소를 물리 주소로 변경하는메모리 관리 장치(MMU)를 통하여 변환됩니다. 메모리 관리 장치(Memory Management Unit, 줄여서 MMU)는 CPU가 메모리에 접근하는 것을 관리하는 컴퓨터 하드웨어 부품입니다. 가상 메모리 주소를 실제 메모리 주소로 변환하며, 메모리 보호, 캐시 관리, 버스 중재 등의 역할을 담당합니다.

MMU와 TLB 구조

MMU와 TLB 구조

- CPU가 실제 데이터를 참조하기 위하여 MMU를 접근하면, MMU에서 DRAM에 있는 Map에 접근하여 실제 주소를 CPU에게 건네줍니다. 이후 CPU가 실제 물리 주소에 접근하게 됩니다. 이렇게 되면 DRAM에 2번 접근을 해야되고, CPU의 속도에 비해 DRAM이 매우 느리기 때문에 시간적 손해를 볼 수 밖에 없습니다. 이를 보완하기 위하여 TLB를 사용합니다.

- 빠른 속도를 확보하기 위하여 MMU는

변환 참조 버퍼(Translation Lookaside Buffer, TLB)라는 고속의 보조기억장치를 참조합니다. 이는 CPU가 DRAM에 접근하는 시간이 오래 걸려 L1 ~ L3 Cache를 사용하는 것과 비슷한 원리입니다. CPU가 MMU에 주소를 요청하면 MMU는 TLB에 Cache가 남아있는지 확인하고 있으면 바로 CPU에게 전해줍니다. 이 경우 DRAM 접근을 1번만 하면 됩니다. - TLB나 페이지 테이블이 실제 메모리 주소를 가져오지 못하는 경우가 있는데, 이를 페이지 실패(page fault)라 합니다.

출처