쉽게 PCIe를 이해할 수 있게 간략한 개념을 적어보았습니다.

PCIe 란?

PCIe 는 범용 목적의 고속 serial I/O bus

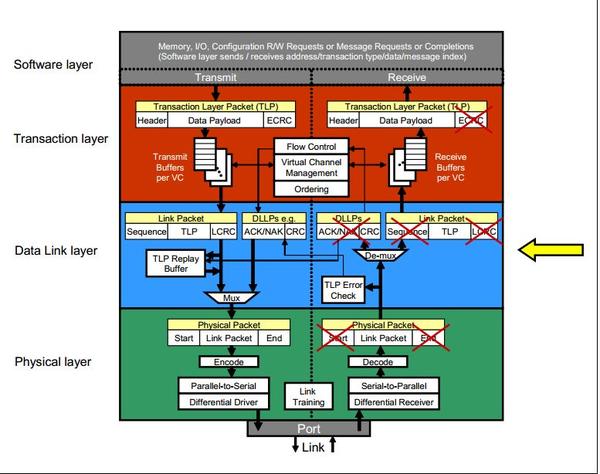

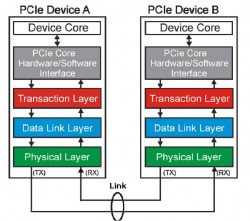

PCIe Layer

아래의 이미지는 PCIe Layer의 이미지입니다.

PCIe Interface - Electrical Pythsical Layer 개념들

De-Emphasis & Pre-Emphasis

- De-emphasis : lowering low frequency

- Pre-emphasis : higher high frequency

Eye Diagram

Link Equalization

- Power on 이나 Reset 시점부터 Link가

정상적인 패킷 교환(normal packet traffic)이 진행 될 수 있도록 L0이 될 때 까지device의 layer, port, link에 관련된 것들을 초기화하는 Physical Layer Control Process. - 하드웨어에 의해 초기화되고, LTSSM(Link Traning & Status State Machine)에 의해 manage됨

- Signal Quality를

향상시키기 위하여 각 Lane의 Transmitter 및 Receiver를 설정 - LTSSM과 관련된 Lane 들은 반드시 Equalization 에 참여해야 함

- 첫 번째 Data Change(8.0GT/s data rate) 에서 수행되야 함

4개의 Equalization Process

- Phase 0 : Gen1(2.5GT/s data rate)에서 시작, TxEQ Preset과 함께 속도 변환 요청. Preset은 device 가 처음 GEN3(8.0GT/s data rate)로 올라갈 때 사용

- Phase 1 : 서로의 Equalization Capability 공유

- Phase 2 : Host의 TX Equalization을 조정

- Phase 3 : Device의 Tx EQualization을 조정

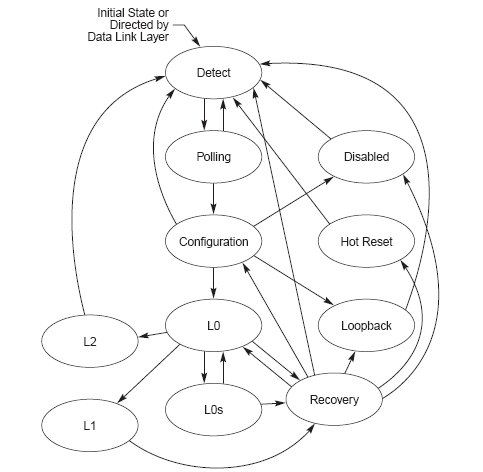

LTSSM(Link Traning & Status State Machine)

- 두 PCIe 디바이스는 Lane의 극성, 링크 혹은 레인의 개수, Equalization, 데이터 속도 등과 같은 요소들을 포함한 다수의 링크 파라미터들과 협상하기 위해 Training Sequences들을 교환

- 아래와 같은 11개의 state 간의 flow 가 존재

Detect

- Reset 후의 initial state

- Link 끝단의 Receiver의 존재를 감지하는 것이 목적

- Detect.Quiet : Transmitter가 Electrical Idle 상태에 진입했을 때

- Detect.Active : Receiver가 연결되어있는지 확인하기 위해 Common Mode Voltage Setting을 통해 각 lane의 연결을 체크

Polling

- Bit lock, Symbol lock, Lane Polarity 등의 정보 공유

- Polling.Active :

- Polling.Compliance :

Configuration

- Link number negotiation, Lane number negotiation 과 같은 condition들을 설정한다.

- Port connect와 그것을 위한 Lane number 들의 assign

Recovery

- 이 단계에서 Transmitter와 Receiver는 설정된 link와 lane number, data rate를 서로 주고 받음

- Operation data rate 변경

- L1 state에서 L0 state로 전환할 때 Recovery 필요

- L0 state에서 high speed로 전환 가능할 때, Link speed/width change 요청

L0

- Data 나 Control Packet을 주고받을 수 있는 Normal operation state

- 모든 Power management state는 L0 으로 부터 진입

Disabled

- Disabled state 진입 후, state 변경이나 Electrical Idle 이 해제될 때 까지 configured 된 link를 disabled 하기 위한 목적

Loopback

- Normal operation에서는 사용하지 않는 test용 state

출처

- http://hardwareverification.weebly.com/pci—express-architecture.html

- http://ssu1945.egloos.com/4007260

- https://blog.asset-intertech.com/test_data_out/2016/11/using-embedded-run-control-for-pcie-link-training-testing.html

NEXTPCIe 구조 및 특징 정리