PCIe Link 에서 L1 PM Substates는 아래와 같이 3가지 state가 있고, 각각 다른 특징을 가집니다. L1.1 substate 들은 제외하고 저전력 L1.2 의 substate 들에 대하여는 그림과 설명을 적어보았습니다.

- L1.0 substate

- Upstream & Downstream Port 에서 Electrical Idle exit을 감지할 수 있어야 합니다.

- L1.1 substate

- Link common mode voltage 유지

- L1.1 state에 들어가기 위하여 bidirectional CLKREQ# signal을 사용합니다.

- Upstream & Downstream Port 에서 Electrical Idle exit을 감지하지 않습니다.

- reference clock이 요구되지 않습니다.

- L1.2 substate

- Link common mode voltage 유지가 요구되지 않습니다.(저전력 상태)

- L1.1 state에 들어가기 위하여 bidirectional CLKREQ# signal을 사용합니다.

- Upstream & Downstream Port 에서 Electrical Idle exit을 감지하지 않습니다.

- reference clock이 요구되지 않습니다.

- LTR(Latency Tolerance Reporting)을 지원해야합니다.

Upstream Port에서 Link가 PCI-PM L1 이나 ASPM L1 state, L2/L3 state일 때, CLKREQ# 를 deassert 할 수 있습니다. 다른 Link state일 때는, Upstream Port 에서 CLKREQ# 를 assert합니다.

1. Entry conditions for L1 PM Substates and L1.0 Requirements

- PCI-PM L1.0 & PCI-PM L1.2 Enable bit 이 Set 되어 있으면, L1.2 substate 는 CLKREQ# 가 deassert 될 때 진입되어야 합니다.

- PCI-PM L1.0 & PCI-PM L1.1 Enable bit 이 Set 되어 있으면, L1.1 substate 는 CLKREQ# 가 deassert 될 때 진입되고 PCI-PM Enable bit는 Clear 되어야 합니다.

- ASPM L1.0 & ASPM L1.2 Enable bit 이 Set 되어 있으면, L1.2 substate 는 CLKREQ# 가 deassert 될 때 진입되어야합니다.

- ASPM L1.0 & ASPM L1.1 Enable bit 이 Set 되어 있으면, L1.1 substate 는 CLKREQ# 가 deassert 될 때 진입되고 L1.2 substate 만족할 수 없습니다.

즉, L1.1 나 L1.2 중 하나의 상태만 지원합니다. L1.2를 들어갈 조건이 만족되면, 아래의 규칙을 따라야합니다.

- Upstream & Downstream Port 는 CLKREQ#를 확인(monitor)해야합니다.

- Upstream Port는 링크가 L1.0 에 들어가기 전까지, CLKREQ#를 deassert 하면 안됩니다.

- 링크가 L1.2로 들어가는 것을 막기 위하여, 양 쪽 Port 중 하나가 CLKREQ# assert를 할 수 있습니다.

- L1.2 로의 진입을 차단하려는 Downstream Port는 링크가 L1에 들어가기 전에 CLKREQ# 를 선언해야합니다.

- CLKREQ #가 deassert 되면 포트는 L1.2로 들어갑니다.

2. L1.2 Requirements

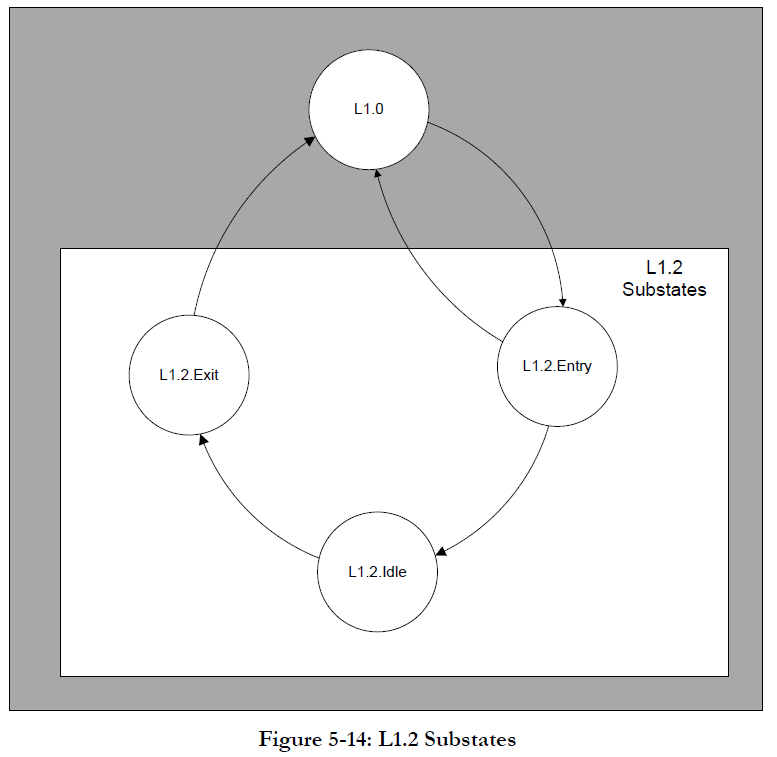

모든 링크와 PHY(Physical Layer) state는 L1.2 동안 유지되거나 종료시 복원되어야 합니다. L1.2 는 크게 3가지 state들(L1.2.Entry, L1.2.Idle, L1.2.Exit)로 나누어져 있습니다.

2.1. L1.2.Entry

L1.2.Entry는 L1.2 로 진입할 때, Refclk이 꺼지는 시간을 허용하고 양 쪽 Port가 CLKREQ# deasserted 된 것을 확인할 수 있게 하는 state입니다. L1.2.Entry는 아래의 규칙을 따라야합니다.

- Upstream & Downstream Port는 commone mode를 유지합니다.

- Upstream & Downstream Port는 electrical idle(EI) exit detect circuitry를 turn off 해야합니다.

- Upstream & Downstream Port는 L1.2.Entry state에서 CLKREQ#를 assert해서는 안됩니다.

- $ T_{\text{L10_REFCLK_OFF}} $ 에서 Refclk을 turn off 해야 합니다.

- 다음 state가 CLKREQ#가 asserted 되면 L1.0이고, 아니라면 $ T_{\text{POWER_OFF}} $를 기다린 후에 L1.2입니다.

2.2. L1.2.Idle

L1.2.Idle state 로 진입하기 위한 요구사항이 만족되면, 포트는 L1.2.Idle state로 진입합니다. L1.2.Idle state는 아래의 조건을 만족해야합니다.

- active logic을 power-down 합니다.

- PHY 의 power 가 제거됩니다.

2.3. L1.2.Exit

- PHY 의 power 가 곧 들어옵니다.

- common mode가 유지될 것입니다.

출처

- PCIe Base 4.0 Spec