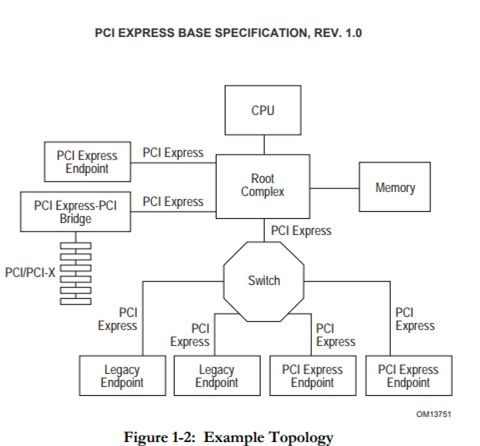

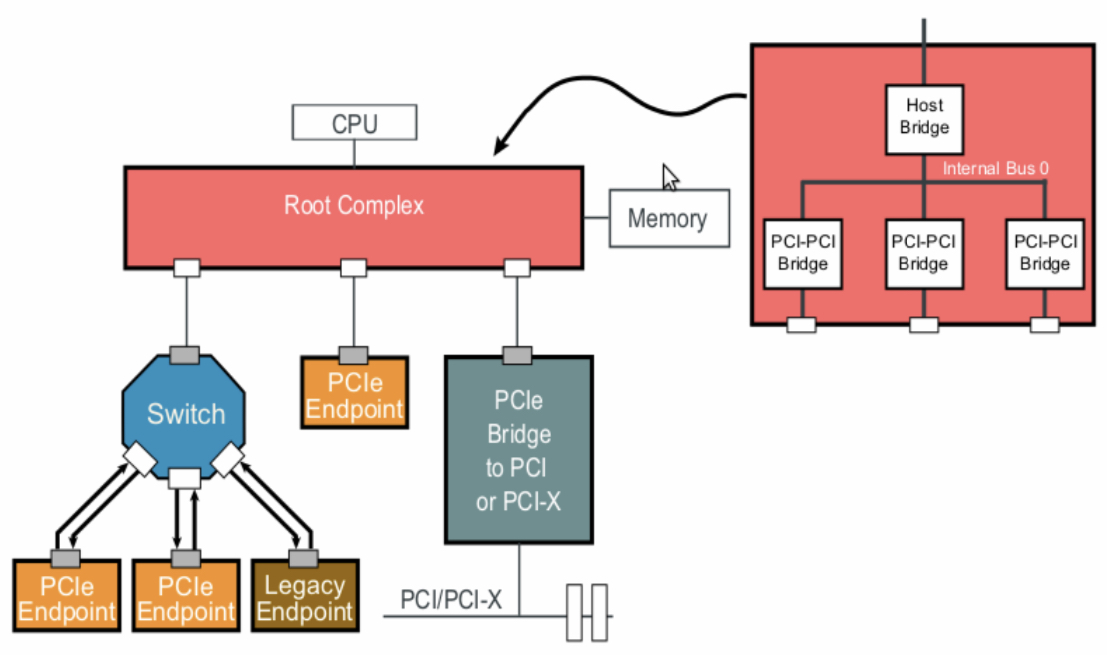

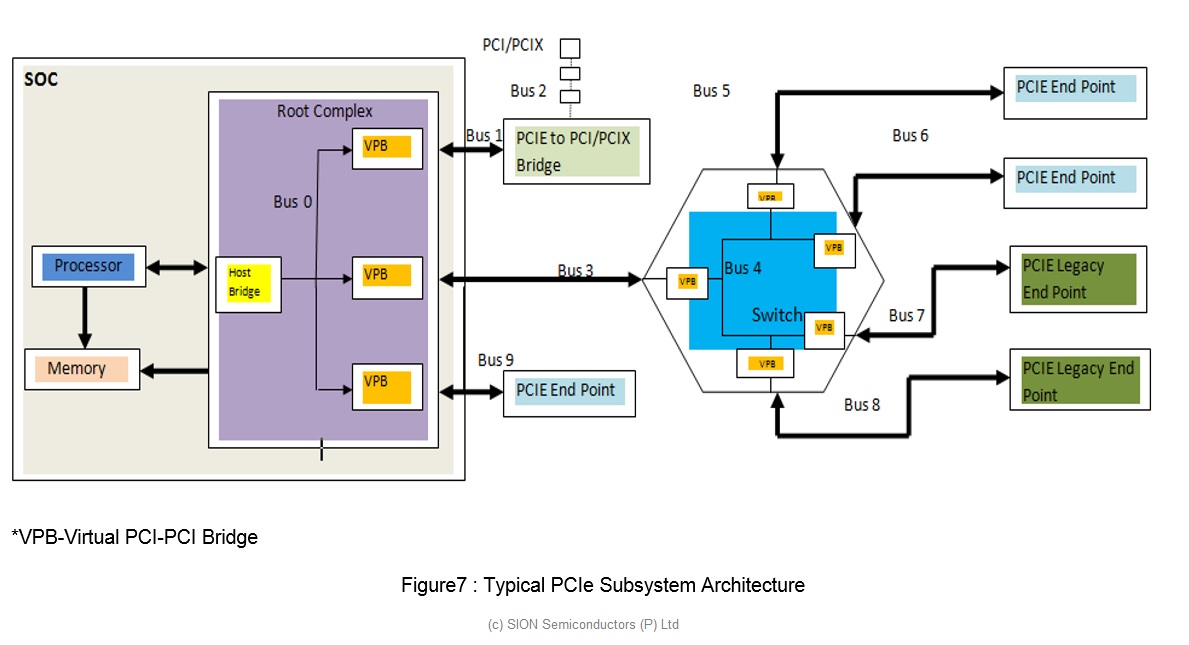

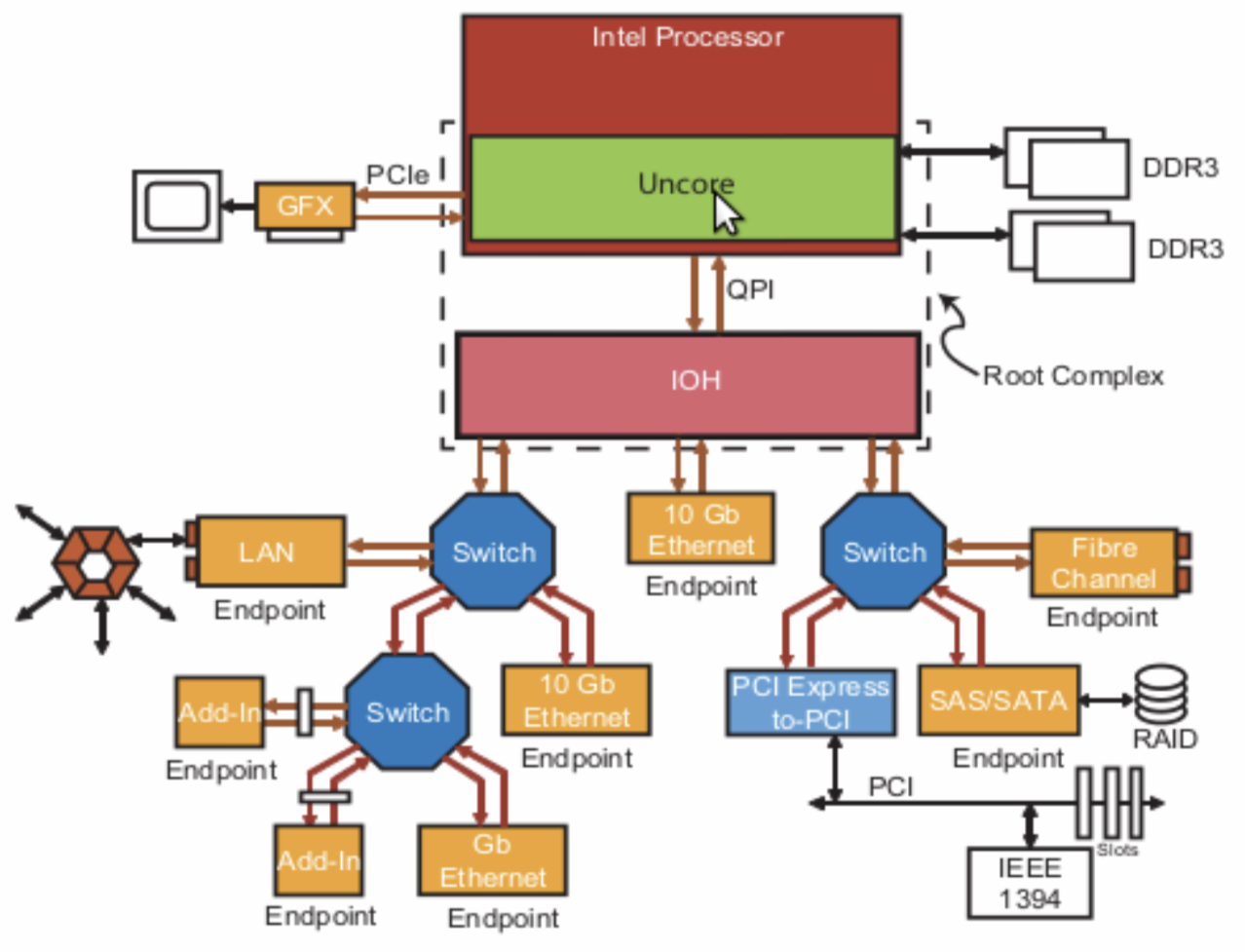

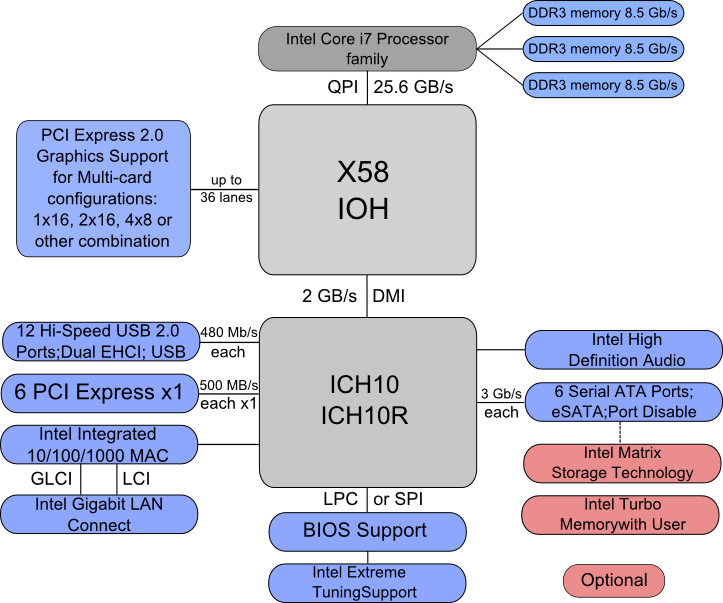

Root Complex

- CPU와 PCIe bus들 사이의 인터페이스(Interface). 인터페이스는 프로세서 인터페이스, DRAM 인터페이스와 같은 여러 구성 요소와 여러 개의 칩들이 포함될 수 있습니다.

- 1개 혹은 그 이상의 PCIe 포트와 Root Port 연결

- PCIe 계층 영역(hierarchy domain)를 하나의 단일 PCIe 계층(hierarchy)으로 논리적으로 결합합니다.

- 계층 구조라고 불려지는 하나의 fabric instance는 다음과 같은 구성요소들로 이루어져 있습니다.

- Rc

- multiple Endpoints(I/O devices)

- Switch

- PCIe to PCI/PCI-X Bridge

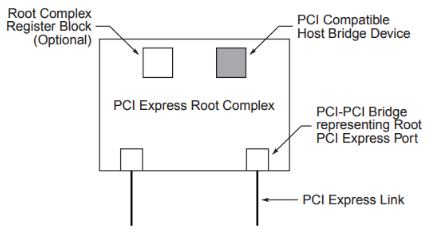

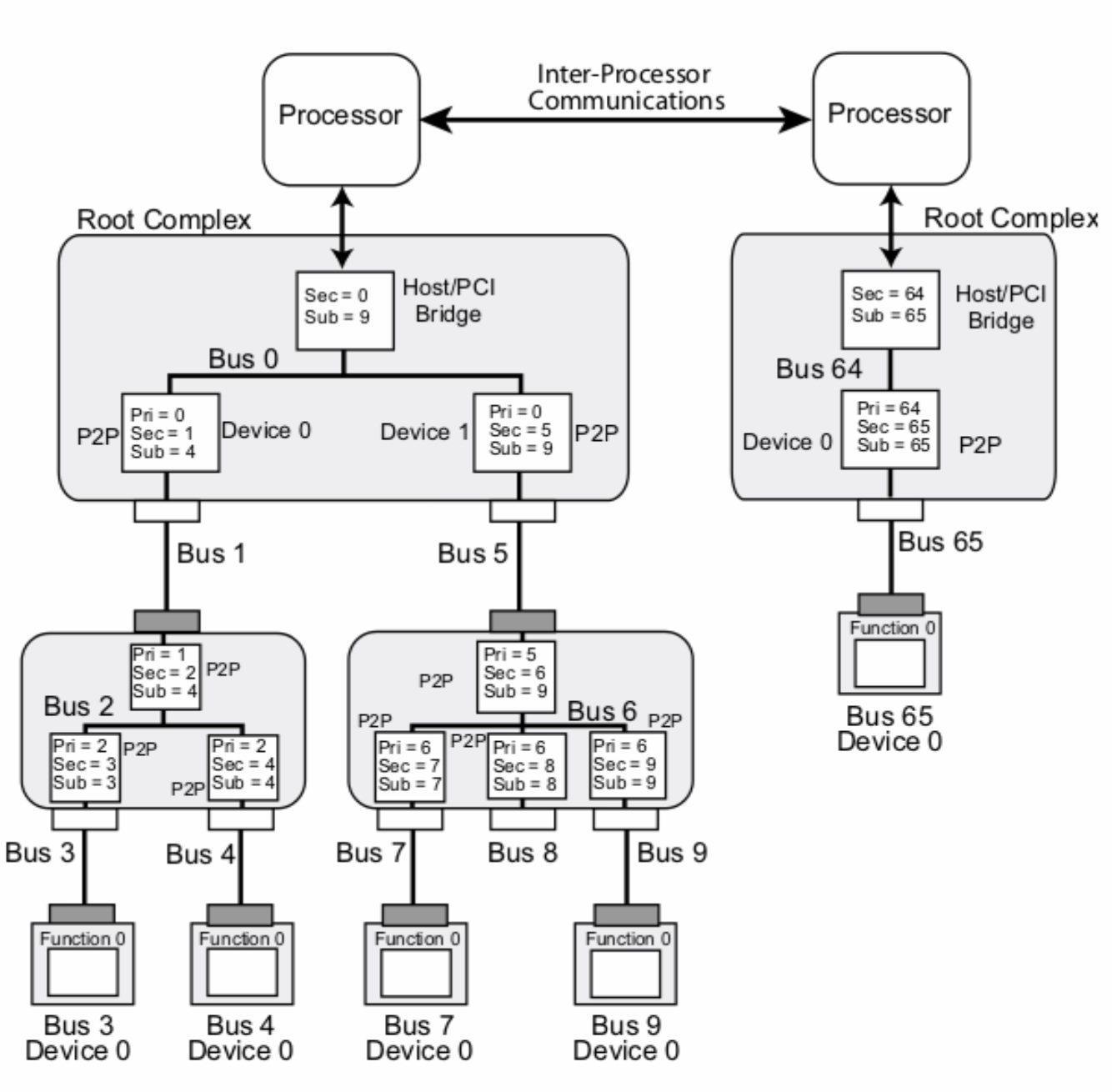

PCIe Root Port

- 연결된 가상 PCI-PCI 브릿지를 통하여 PCIe 상호 연결 계층 구조의 일부를 구성하는 Root Complex 안의 PCIe Port.

- 각각의 Root Port는 분리된 계층 영역을 가지고 있습니다.

- 각각의 계층 영역은 하나의 Endpoint로 구성될 수도 있고, 한 개 이상의 Switch나 Endpoints로 구성된 sub-계층(sub-hierarchy)을 가지고 있을 수도 있습니다.

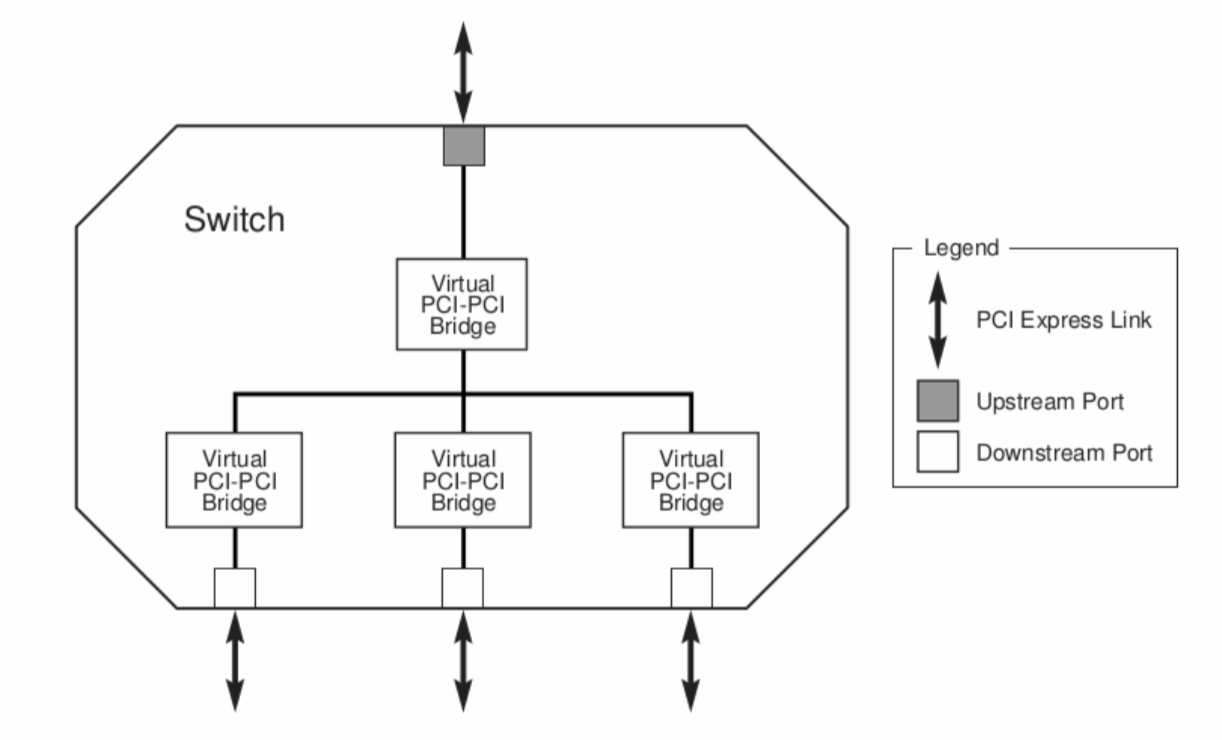

Switch and Bridge

Switch

- 스위치는 하나의 단일 Root Port에 여러 디바이스가 붙을 수 있는 장치입니다. Packet router 처럼 동작하고, 해당 packet의 주소와 다른 routing 정보를 통하여 어떤 경로로 packet이 가야하는지 인식합니다.

- 스위치는 여러 개의 Downstream Ports를 가지고 있지만, Upstream Port는 하나입니다.

Bridge

브릿지는 다른 버스와의 인터페이스를 제공합니다. 해당 인터페이스는 PCI, PCI-X 혹은 다른 PCIe bus 입니다.

PCIe Endpoint Device

- Endpoint Device는 tree topology에서 가장 하위에 위치하고 있으며, 하나의 Upstream Port만 가지고 있습니다.

- Type 0 Configuration Space Header를 가지고 있습니다.

- Switch나 Bridge는 버스 위에서 PCIe transaction의 initiator나 completer 역할을 하지 않습니다. Endpoint Device는 자체적이나 Non-PCIe device를 대신해서 PCIe transaction의 Requester 혹은 Completer가 될 수 있는 장치 유형입니다. (ex> PCIe 연결 그래픽 컨트롤러, PCIe-USB 인터페이스 등)

- MSI/MSI-X를 지원합니다.

- Endpoint 디바이스에는 아래의 3가지 종류가 있습니다.

- Legacy PCI Endpoint

- I/O 요청 제공 및 발생 가능

- 4G 주소를 초과하는 메모리 트랜잭션 불가능(32bit Address Register)

- PCIe Endpoint

- I/O 요청 발생시키면 안됨

- 4G 주소를 초과하는 메모리 트랜잭션 가능

- Root Complex Integrated Endpoint

- Root Complex 내부 로직에 구현된 루트 포트

- I/O 요청 발생시키면 안됨

- 전원 관리 구현 X

- Hot Plug 지원 X

- Legacy PCI Endpoint

Enumeration

- Enumeration은 configuration software가 시스템 topology를 발견하고, bus number와 시스템 자원을 할당하는 과정입니다.

- x86 PCIe 아키텍처에서는 enumeration은 BIOS 하드웨어 초기화 과정에서 이루어집니다. 모든 레지스터들은 부트로더 이전에 설정됩니다.

- system software는 enumeration 규칙에 따라서 enumeration을 재할당 할 수 있습니다.

참고 이미지

출처

- https://webcourse.cs.technion.ac.il/236376/Spring2016/ho/WCFiles/chipset_microarch.pdf

- http://blog.naver.com/PostView.nhn?blogId=joa_quin&logNo=221285262754&categoryNo=15&parentCategoryNo=0&viewDate=¤tPage=1&postListTopCurrentPage=1&from=postView&userTopListOpen=true&userTopListCount=5&userTopListManageOpen=false&userTopListCurrentPage=1

- http://www.sionsemi.com/whitepapers/pcie-overview.html

- http://jake.dothome.co.kr/pci-1/

- https://en.wikipedia.org/wiki/Intel_X58#/media/File:X58_Block_Diagram.png